目录

PN结

MOSFET基础

LTPS制程中影响晶体管参数的工艺

TFT器件可靠性

UISL基本制程工艺(65nm)

1.PN结如何形成

当n型半导体与p型半导体接触时,电子与空穴都从浓度高处向浓度低处扩散,称为扩散运动。当电子进入p型区域,空穴进入n型区域后,即与对方多子复合,留下了固定不动的原子核。这些原子核形成了一个内建电场,使电子与空穴向反方向漂移。这两种运动达到平衡时的结果就是形成一段没有载流子的区域,称为空间电荷区,也叫耗尽层。这个空间电荷区叫做PN结。

PN结的伏安特性

当PN正向偏置时,电流随电压的增大而迅速增大。当反向偏置时,电流很小且随电压增大变化不大,但是当电压达到临界点时电流突然增大。这两种现象称为正向导通与反向导击穿。

正向与反向偏置的定义:P型半导体电位高于n型半导体电位,称为正向偏置。反之为反向偏置。PN结的伏安特性的解释当PN结正向偏置时,外部电场从P型指向N型区,使得空穴和电子都向界面处运动。因此耗尽层厚度变窄,电流上升。同理反向偏置时耗尽层变宽,阻碍电流的通过,因此电流随电压变化很小。

正向与反向偏置的定义:P型半导体电位高于n型半导体电位,称为正向偏置。反之为反向偏置。PN结的伏安特性的解释当PN结正向偏置时,外部电场从P型指向N型区,使得空穴和电子都向界面处运动。因此耗尽层厚度变窄,电流上升。同理反向偏置时耗尽层变宽,阻碍电流的通过,因此电流随电压变化很小。

当反向电压达到一定强度时,PN结电流急剧增大,称为反向击穿。这时的电压叫击穿电压。反向击穿的模式有了两种

齐纳击穿:发生在高浓度掺杂,耗尽层很窄时。此时耗尽层内电场强度高,能够破坏共价键结构形成电子-空穴对。(E>1MV/cm)

雪崩击穿:发生在中低浓度掺杂,耗尽层较宽时。电子在电场中获得能量,如果电场强度足够大,电子与晶格碰撞后就可以破坏共价键,产生电子-空穴对。产生的电子和空穴又与晶格碰撞生成新的电子-空穴对。该过程称为雪崩倍增。(E~0.2-0.6MV/cm)PN结电容PN结电容分为两部分:势垒电容和扩散电容

PN结负偏压时,耗尽层宽度随电压变化,空间电荷区的电荷数量也随之变化。电压向负方向变化时耗尽层变宽,空间电荷增加,相当于充电,向正方向变化则耗尽层变窄,电荷数量减少,相当于放电。该电容称为势垒电容,它是由多子变化引起的。

PN结正偏时,P区和N区分别向对方注入空穴和电子,这些载流子在对方体内称为非平和少数载流子。当电压变化时,在PN结两侧的少子数量发生变化,相当于对电容进行放电。该电容称为扩散电容,它是由少子变化引起的。负偏压时由于平衡少子数量少,该电容忽略不计。而且由于少子寿命的限制,高频下扩散电容不起作用。

由此可见PN结电容并不是一个固定值,它随外电压的变化而变化。2.MOSFET及相关器件

MOS二极管是MOSFET的基础,在电路中也被用作电容。它是研究半导体表面特性最有用的器件之一。

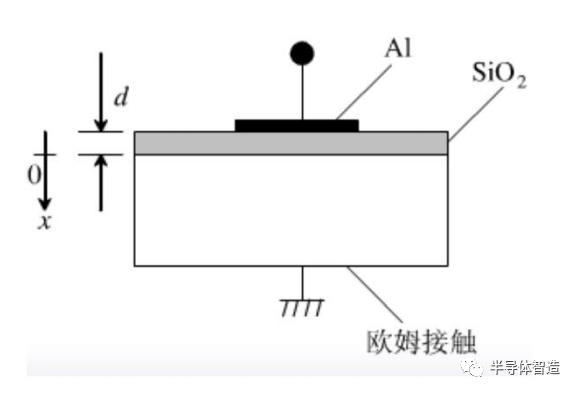

理想MOS二极管的结构图如下图所示。d为氧化层厚度,V为金属电极上的电压。定义金属电极上电位高于体电位时为正偏压。 MOS二极管特性

MOS二极管特性

当MOS管施加正或负偏压时,在Si表面有电子或空穴积聚。为讨论方便,以下以P型半导体为例进行说明。

当MOS管为负偏压时,Si表面积聚了比体内更多的空穴,此时为积累状态。

当偏压由负转正时,空穴被排离表面而作为少子的电子则被吸引到表面。电子与空穴复合的结果是表面载流子浓度较少直至消失,硅表面出现耗尽层,此时为耗尽状态。

正偏压继续增大时,表面的电子浓度超过了空穴浓度从而形成一个自由电子层,这个电子薄层称为反型层。此时为反型状态。

继续增大偏压,反型层厚度随之增加。

N型半导体依此类推。MOS二极管电容MOS二极管本质上是一个电容器。与理想电容器不同的是,它的下极板是半导体,因此MOS电容并不是一个定值,而是随栅极偏压而变化的。下图是P-Si MOS二极管的C-V曲线 当Vg为负时,硅表面为P型,测得的电容即为栅氧化层的电容。当Vg向正移动时,硅表面的空穴逐渐减少而电子逐渐增多,在表面形成耗尽层且耗尽层不断变厚。因此电容逐渐下降。当耗尽层达到最宽,即将出现反型时电容达到最小值。反型后由于反型层中电子对电场的屏蔽,耗尽层宽度不再变化,因此电容值不再改变。MOSFET基本结构MOSFET全称metal-Oxide-Semiconductor Field Effect Transistor.MOS表示器件的基本结构,FET表示器件的工作原理。

当Vg为负时,硅表面为P型,测得的电容即为栅氧化层的电容。当Vg向正移动时,硅表面的空穴逐渐减少而电子逐渐增多,在表面形成耗尽层且耗尽层不断变厚。因此电容逐渐下降。当耗尽层达到最宽,即将出现反型时电容达到最小值。反型后由于反型层中电子对电场的屏蔽,耗尽层宽度不再变化,因此电容值不再改变。MOSFET基本结构MOSFET全称metal-Oxide-Semiconductor Field Effect Transistor.MOS表示器件的基本结构,FET表示器件的工作原理。 MOSFET伏安特性MOSFET是在MOS二极管的基础上加入了源漏两端构成的。源漏两端的掺杂是和沟道区相反的,从而构成了两个背靠背的PN结。在栅极无偏压时,从漏到源只有很小的PN结反向漏电流。当栅极上加电压时,源漏电流会随之有明显变化。因此叫场效应管。

MOSFET伏安特性MOSFET是在MOS二极管的基础上加入了源漏两端构成的。源漏两端的掺杂是和沟道区相反的,从而构成了两个背靠背的PN结。在栅极无偏压时,从漏到源只有很小的PN结反向漏电流。当栅极上加电压时,源漏电流会随之有明显变化。因此叫场效应管。

MOS管源漏电流主要受栅极电压和漏极电压的控制。下面以NMOS为例说明电流和栅极电压与漏极电压的关系。

MOSFET转移特性随着栅极正偏电压逐渐增大,硅表面电子逐渐增多最后形成一个N型的反型层。反型层与同为N型的漏源连通,形成导电沟道。这时如果给漏极加电压,就会有电流流过。沟道从无到有时所需的栅极电压VG定义为阈值电压VT。 漏源电流Ids随栅极电压Vg的变化如下图当VG<VT时沟道未形 成,MOS管处于截止状态,lds很小。当VG>VT时, 沟道开启且沟道厚度随VG增大而变大。因此lds随VG增大而迅速增大。当VG略小于VT时, Ids随VG呈指数关系变化。这一小段区间称为亚阀值区域。VG增大到一定程度时,lds增加幅度变小。

漏源电流Ids随栅极电压Vg的变化如下图当VG<VT时沟道未形 成,MOS管处于截止状态,lds很小。当VG>VT时, 沟道开启且沟道厚度随VG增大而变大。因此lds随VG增大而迅速增大。当VG略小于VT时, Ids随VG呈指数关系变化。这一小段区间称为亚阀值区域。VG增大到一定程度时,lds增加幅度变小。 MOSFET输出特性漏源电流lds随漏极电压Vd的变化如下图当VG<VT时沟道未形成,MOS管处于截止状态,lds随Vd变化很小。

MOSFET输出特性漏源电流lds随漏极电压Vd的变化如下图当VG<VT时沟道未形成,MOS管处于截止状态,lds随Vd变化很小。

当VG>VT时,沟道形成,有较大的电流通过且电流随Vd增大而增大。(线性区)

当Vd增大到一定程度时,ld变化趋于饱和。( 饱和区)

Vd继续增大,电流将急剧上升。(击穿) 线性区在MOS二级管中,反型层的厚度是均匀的。但是在MOSFET中,当Vds不为零时,在反型层中沿着沟道方向的电位是不均匀的,造成栅氧化层两端的电压并不等于Vg。结果是沟道的厚度从漏极到源极是不一致的。当Vd较小时,沟道厚度的这种不一 致不会带来大的影响,MOS管呈现电阻特性。反映在Id-Vd曲线上就是线性区。

线性区在MOS二级管中,反型层的厚度是均匀的。但是在MOSFET中,当Vds不为零时,在反型层中沿着沟道方向的电位是不均匀的,造成栅氧化层两端的电压并不等于Vg。结果是沟道的厚度从漏极到源极是不一致的。当Vd较小时,沟道厚度的这种不一 致不会带来大的影响,MOS管呈现电阻特性。反映在Id-Vd曲线上就是线性区。 饱和区沟道在漏极一端的电位近似于Vd,栅极与沟道内的真正电位差为Vg-Vd.而在源极一端。因为多数情况下源极电位为零,电位差即为Vg。所以从源极到漏极沟道厚度逐渐变窄。当Vd逐渐增大,直到Vd=Vg-VT时,沟道消失。这种现象称为夹断。

饱和区沟道在漏极一端的电位近似于Vd,栅极与沟道内的真正电位差为Vg-Vd.而在源极一端。因为多数情况下源极电位为零,电位差即为Vg。所以从源极到漏极沟道厚度逐渐变窄。当Vd逐渐增大,直到Vd=Vg-VT时,沟道消失。这种现象称为夹断。 在夹断发生后继续增大Vd,夹断区扩展而有效沟道长度变短。增加的电压几乎全部落在夹断区上,所以Id变化不大。对应的Id-Vd曲线进入饱和区。夹断区的导电原理:在夹断区耗尽层与栅氧化层接触,载流子数量非常少。但是从源区注入的电子会在强电场的作用下被拉到漏极,这就是夹断区的导电方式。MOS管击穿当VD继续增大时,MOS管被击穿,电流急剧增大。主要有两种击穿方式:雪崩击穿。实际上就是漏极和衬底的PN结击穿。漏源穿通。漏极的耗尽层随Vo增大而变宽,当漏极耗尽层与源极耗尽层连通时,源极的电子注入并被耗尽层中的电场拉到漏极。产生漏电。实际的MOSFET电容C-V曲线与MOS二极管不同,MOSFET的栅氧化层电容在高频与低频测试条件下呈现不同的CV曲线。高频测试时,其曲线在负偏压部分和理论值基本相同。在反型层出现后,电容并不像理论上那样保持在最小值,而是进一步下降。这是因为半导体进入深耗尽状态,原因是少子的产生需要定时间,如果测试信号的频率过高,少子产生速度会跟不上振荡频率,从而使得感应电荷数量减少,电容值变小。低频测试时,负偏压部分的曲线无变化。当反型层产生后,少子的产生速度可以跟上测试信号变化,因此电容又迅速变大,直至和负偏压时基本相当。对于薄膜晶体管这样的三 端器件,其C-V曲线又有所不同。

在夹断发生后继续增大Vd,夹断区扩展而有效沟道长度变短。增加的电压几乎全部落在夹断区上,所以Id变化不大。对应的Id-Vd曲线进入饱和区。夹断区的导电原理:在夹断区耗尽层与栅氧化层接触,载流子数量非常少。但是从源区注入的电子会在强电场的作用下被拉到漏极,这就是夹断区的导电方式。MOS管击穿当VD继续增大时,MOS管被击穿,电流急剧增大。主要有两种击穿方式:雪崩击穿。实际上就是漏极和衬底的PN结击穿。漏源穿通。漏极的耗尽层随Vo增大而变宽,当漏极耗尽层与源极耗尽层连通时,源极的电子注入并被耗尽层中的电场拉到漏极。产生漏电。实际的MOSFET电容C-V曲线与MOS二极管不同,MOSFET的栅氧化层电容在高频与低频测试条件下呈现不同的CV曲线。高频测试时,其曲线在负偏压部分和理论值基本相同。在反型层出现后,电容并不像理论上那样保持在最小值,而是进一步下降。这是因为半导体进入深耗尽状态,原因是少子的产生需要定时间,如果测试信号的频率过高,少子产生速度会跟不上振荡频率,从而使得感应电荷数量减少,电容值变小。低频测试时,负偏压部分的曲线无变化。当反型层产生后,少子的产生速度可以跟上测试信号变化,因此电容又迅速变大,直至和负偏压时基本相当。对于薄膜晶体管这样的三 端器件,其C-V曲线又有所不同。 为什么需要LDD热载流子效应(Hot Carrier)热载流子就是具有较高能量的载流子。当S/D重掺 杂时,耗尽层宽度窄而其中的电场强度高。部分电子会获得足够高的能量然后在与晶格碰撞时产生新的电子空穴对,并形成正反馈产生更多的电子-空穴对。这些新产生的电子空穴对都是载流子,因此造成饱和电流增加(kink effect),和可靠性变差(进入GI或破坏界面处的Si-H键)。LDD即在重掺杂漏极与沟道之间插入一个轻掺杂漏极,这样耗尽层宽度增加,降低热载流子发生率。耗尽层宽度增加的另一个好处就是降低漏电流(Ioff)但是相应的代价是开态电流(lon)下降。NMOS的hot carrier比PMOS严重, 这是因为NMOS的载流子是电子,而电子的有效质量约为空穴的一半。讨论:影响器件特性的因素LTPS制程回顾影响实际VT的因素有哪些0影响实际lon的因素有哪些影响loff的因素有哪些影响μ和SS的因素有哪些LTPS工艺对器件参数的影响LTPS制程中制造的MOS管与以上论述的标准MOS管最大的不同在于LTPS的器件是在一层多晶硅薄膜中制造的,因此它是一个三端器件(无衬底引出)。由此造成的结果是体电位受栅极电压和漏极电压影响而不固定。尽管如此,很多情况下薄膜晶体管的伏安曲线还是接近标准MOS管的,影响器件特性的工艺也基本相同。但LTPS有个独有的氢化工艺,其对TFT影响非常大。该工艺的目的是将氢掺入多晶硅中,与多晶硅体内的悬挂键形成Si-H键来修补晶格缺陷。氢化效果的好坏对所有的晶体管参数都有影响。除此之外,各项参数的主要影响因素如下:VT: 主要受沟道区掺杂浓度、栅电容、界面态与氧化层电容影响。III/V族元素污染和金属离子污染也会显著影响VT。Plasma Induced Damage也会有很大影响。lon: 主要受沟道区掺杂浓度、栅电容、LDD/SD浓度及Overlay的影响。多晶硅晶粒大小,表面粗糙度及界面态也是主要影响因素。此外还有Gate和polyCD。loff: 主要受沟道与LDD/SD杂质浓度及分布影响: Gate CD和LDD/SDOverlay会有较大影响。栅氧化层厚度不均匀或质量差时,栅极漏电也会是一个重要分量。对于没有LDD的晶体管,GIDL也很重要。SS:结漏电、栅电容、沟道反型层电容。U:沟道掺杂浓度、LDD/SD浓度、栅氧化层的界面态、多晶硅晶粒尺寸。等离子体损伤等离子体在半导体加工工艺中十分常见,主要用于CVD、Dry Etch、 PR removal等。在使用等离子体工艺对基板加工时,这些具有一定能量的离子会运动到基板表面,并与基板发生化学反应或者物理轰击作用,从而对表面造成一定的损伤。这种损伤叫做等离子体损伤(Plasma Damage)。等离子体损伤最为典型的就是对沟道区的硅晶格损伤导致VT漂移和迁移率下降。实例: ashing引起的Plasma Damage。等离子体诱导损伤等离子体工艺使用带电离子对材料进行加工时,这些离子会将所携带的电荷传递基板。如果没有释放路径,这些电荷会积累在基板表面,并随着图形的不同在各个区域建立不同的电位。等离子体诱导损伤(Plasma Induced Damage,简称PID)特指这些积聚的电荷引起局部电位升高从而对器件造成了损伤。实例: PV dry etch引起的PID3.TFT器件可靠性的测量为了推算TFT器件的寿命,通常在高温和高电压下对晶体管进行Stress测试,通过观察一定时间后的器件特性变化情况来推算其寿命。通常进行的测试项目有TDDB (Time Dependent Dielectric Breakdown)指栅极电压小于击穿电压时,经过长时间的加压而使栅绝缘层发生击穿。测试方法为将电压加至工作电压的1.1-1.5倍,经过一段时间后测量栅极漏电的变化。NBTI (Negative Bias Temperature Instability)PMOS在负偏压情况下空穴与Si表面的Si-H键作用生成H原子进而产生H2扩散,而留下的Si悬挂键则使得Vth发生偏移。测试方法为加高温、高栅极电压后测量Vth的变化。

为什么需要LDD热载流子效应(Hot Carrier)热载流子就是具有较高能量的载流子。当S/D重掺 杂时,耗尽层宽度窄而其中的电场强度高。部分电子会获得足够高的能量然后在与晶格碰撞时产生新的电子空穴对,并形成正反馈产生更多的电子-空穴对。这些新产生的电子空穴对都是载流子,因此造成饱和电流增加(kink effect),和可靠性变差(进入GI或破坏界面处的Si-H键)。LDD即在重掺杂漏极与沟道之间插入一个轻掺杂漏极,这样耗尽层宽度增加,降低热载流子发生率。耗尽层宽度增加的另一个好处就是降低漏电流(Ioff)但是相应的代价是开态电流(lon)下降。NMOS的hot carrier比PMOS严重, 这是因为NMOS的载流子是电子,而电子的有效质量约为空穴的一半。讨论:影响器件特性的因素LTPS制程回顾影响实际VT的因素有哪些0影响实际lon的因素有哪些影响loff的因素有哪些影响μ和SS的因素有哪些LTPS工艺对器件参数的影响LTPS制程中制造的MOS管与以上论述的标准MOS管最大的不同在于LTPS的器件是在一层多晶硅薄膜中制造的,因此它是一个三端器件(无衬底引出)。由此造成的结果是体电位受栅极电压和漏极电压影响而不固定。尽管如此,很多情况下薄膜晶体管的伏安曲线还是接近标准MOS管的,影响器件特性的工艺也基本相同。但LTPS有个独有的氢化工艺,其对TFT影响非常大。该工艺的目的是将氢掺入多晶硅中,与多晶硅体内的悬挂键形成Si-H键来修补晶格缺陷。氢化效果的好坏对所有的晶体管参数都有影响。除此之外,各项参数的主要影响因素如下:VT: 主要受沟道区掺杂浓度、栅电容、界面态与氧化层电容影响。III/V族元素污染和金属离子污染也会显著影响VT。Plasma Induced Damage也会有很大影响。lon: 主要受沟道区掺杂浓度、栅电容、LDD/SD浓度及Overlay的影响。多晶硅晶粒大小,表面粗糙度及界面态也是主要影响因素。此外还有Gate和polyCD。loff: 主要受沟道与LDD/SD杂质浓度及分布影响: Gate CD和LDD/SDOverlay会有较大影响。栅氧化层厚度不均匀或质量差时,栅极漏电也会是一个重要分量。对于没有LDD的晶体管,GIDL也很重要。SS:结漏电、栅电容、沟道反型层电容。U:沟道掺杂浓度、LDD/SD浓度、栅氧化层的界面态、多晶硅晶粒尺寸。等离子体损伤等离子体在半导体加工工艺中十分常见,主要用于CVD、Dry Etch、 PR removal等。在使用等离子体工艺对基板加工时,这些具有一定能量的离子会运动到基板表面,并与基板发生化学反应或者物理轰击作用,从而对表面造成一定的损伤。这种损伤叫做等离子体损伤(Plasma Damage)。等离子体损伤最为典型的就是对沟道区的硅晶格损伤导致VT漂移和迁移率下降。实例: ashing引起的Plasma Damage。等离子体诱导损伤等离子体工艺使用带电离子对材料进行加工时,这些离子会将所携带的电荷传递基板。如果没有释放路径,这些电荷会积累在基板表面,并随着图形的不同在各个区域建立不同的电位。等离子体诱导损伤(Plasma Induced Damage,简称PID)特指这些积聚的电荷引起局部电位升高从而对器件造成了损伤。实例: PV dry etch引起的PID3.TFT器件可靠性的测量为了推算TFT器件的寿命,通常在高温和高电压下对晶体管进行Stress测试,通过观察一定时间后的器件特性变化情况来推算其寿命。通常进行的测试项目有TDDB (Time Dependent Dielectric Breakdown)指栅极电压小于击穿电压时,经过长时间的加压而使栅绝缘层发生击穿。测试方法为将电压加至工作电压的1.1-1.5倍,经过一段时间后测量栅极漏电的变化。NBTI (Negative Bias Temperature Instability)PMOS在负偏压情况下空穴与Si表面的Si-H键作用生成H原子进而产生H2扩散,而留下的Si悬挂键则使得Vth发生偏移。测试方法为加高温、高栅极电压后测量Vth的变化。

HCI (Hot carrie Injection)

热载流子注入至GI膜内引起的Vth偏移。测试方法为加VD=VG=1.1-1.5工作电压使TFT长时间处于导通状态下后测量Vth和Ion变化。Non-conductive HCI晶体管处于截止状态时的HCI效应。测试方法为加VD=1.1-1.5工作电压而VG=0,一段时间后测量Vth和lon变化。用于OLED驱动的TFT需要在带负载和不带负载(负载及发光单元)的情况下分别测量可靠性,并使用模拟实际显示情况下的脉冲加压法。4.半导体逻辑器件工艺流程简介(65nm) fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Shallow Trench Isolation

Shallow Trench Isolation fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Well Formation

Well Formation fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Gate Oxide

Gate Oxide fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Poly Gate

Poly Gate fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) LDD & Halo Formation

LDD & Halo Formation fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Spacer

Spacer fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) S/D Formation

S/D Formation fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Stress Engineering

Stress Engineering fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Salicide(Self-aligned Silicide)

Salicide(Self-aligned Silicide) fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) ILD & Contact

ILD & Contact fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) 1st Cu Inter-Connection

1st Cu Inter-Connection fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) Via1/metal2 and Above

Via1/metal2 and Above fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E)

*本文来源:半导体智造

fill=%23FFFFFF%3E%3Crect x=249 y=126 width=1 height=1%3E%3C/rect%3E%3C/g%3E%3C/g%3E%3C/svg%3E) 欢迎留言,分享观点。为作者打call,点亮右下角“赞”和“在看”↓↓↓

欢迎留言,分享观点。为作者打call,点亮右下角“赞”和“在看”↓↓↓